# Dynamic Observation of Phase Transformation Behaviors in Indium(III) Selenide Nanowire Based Phase Change Memory

Yu-Ting Huang,<sup>†</sup> Chun-Wei Huang,<sup>†</sup> Jui-Yuan Chen,<sup>†</sup> Yi-Hsin Ting,<sup>†</sup> Kuo-Chang Lu,<sup>‡</sup> Yu-Lun Chueh,<sup>§</sup> and Wen-Wei Wu<sup>†,\*</sup>

<sup>†</sup>Department of Materials Science and Engineering, National Chiao Tung University, No. 1001, University Road, Hsinchu 300, Taiwan, <sup>‡</sup>Department of Materials Science and Engineering, National Cheng Kung University, Tainan 701, Taiwan, and <sup>§</sup>Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu 300, Taiwan

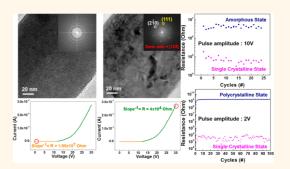

**ABSTRACT** Phase change random access memory (PCRAM) has been extensively investigated for its potential applications in next-generation nonvolatile memory. In this study, indium(III) selenide (In<sub>2</sub>Se<sub>3</sub>) was selected due to its high resistivity ratio and lower programming current. Au/In<sub>2</sub>Se<sub>3</sub>-nanowire/Au phase change memory devices were fabricated and measured systematically in an *in situ* transmission electron microscope to perform a RESET/SET process under pulsed and dc voltage swept mode, respectively. During the switching, we observed the dynamic evolution of the phase transformation process. The switching behavior resulted from crystalline/amorphous change and revealed that a long pulse width

would induce the amorphous or polycrystalline state by different pulse amplitudes, supporting the improvement of the writing speed, retention, and endurance of PCRAM.

**KEYWORDS:** phase change · PCRAM · nanodevices · *in situ* TEM · nonvolatile memory · In<sub>2</sub>Se<sub>3</sub>

n the past decade, the dimensions of device structures have been miniaturized and followed Moore's law for better performance. One of the nonvolatile functionalities for the next generation was proposed to be phase change memory. With its simple structure, high density, fast speed, scaling limit, and low power consumption, phase change random access memory (PCRAM) is a potential candidate for replacing flash memory. The structure of PCRAM was composed of a phase change material, such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST), AgInSbTe, or In<sub>2</sub>Se<sub>3</sub>, sandwiched between two electrodes. Among them, In<sub>2</sub>Se<sub>3</sub> is of high resistivity ratio and lower programing current compared with GST.<sup>1–6</sup> It has two kinds of typical structures, vertical cell/thin film PRAM and horizontal cell/nanowire memory.<sup>7</sup> The former has a heater at the bottom, which is surrounded by dielectric materials and is easy to produce. The latter has high scalability, is selfassembled, and has reduced thermal budget and power consumption due to the smaller volume.<sup>2,4,8–13</sup> The heated area of the nanowire-based horizontal cell is confined to the phase change material, and the evolution of the phase change process could be observed and studied easily.<sup>7</sup>

Chalcogenide, the universal phase change material, has two polymorphic states, amorphous and crystalline. The amorphous state has a higher resistance for its short atomic range order, low free electron density, and high activation energy, while the crystalline state has lower resistance for its long-range atomic order, high free electron density, and low activation energy.<sup>8</sup> The switching of these two states is the important operation for the memory. In order to induce the phase transition, a high voltage and short pulse were applied to cause the crystalline state to switch to the amorphous state, while a low voltage and long pulse were applied to turn the amorphous state to a crystalline state.6

\* Address correspondence to wwwu@mail.nctu.edu.tw.

Received for review July 1, 2014 and accepted August 18, 2014.

Published online August 18, 2014 10.1021/nn503576x

© 2014 American Chemical Society

VOL. 8 • NO. 9 • 9457-9462 • 2014

ARTICLE

The basic mechanism has been studied to improve the characteristics of PCRAM.<sup>14</sup> However, the correlation between electrical behaviors and the evolution of the polymorphism is still unclear. In this work, we studied the real-time switching behavior of  $In_2Se_3$ nanowire-based PCRAM in an *in situ* TEM. The evolution of the nanostructure within a nanowire was observed during the SET and RESET processes by pulsed and dc modes. This observation demonstrated that a long pulse width would induce the amorphous or polycrystalline state by different pulse amplitudes, providing the information to improve the writing speed, retention, and endurance of the PCRAM.

## **RESULTS AND DISCUSSION**

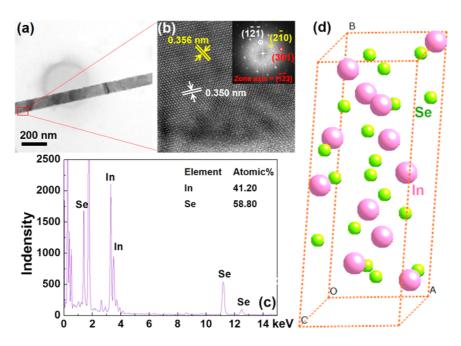

The structure and chemical composition of In<sub>2</sub>Se<sub>3</sub> nanowires were identified by transmission electron microscopy (TEM), energy-dispersive X-ray spectroscopy (EDS), and X-ray diffraction (XRD). The TEM image in Figure 1a shows that the diameter and the length of the In<sub>2</sub>Se<sub>3</sub> nanowire were about 50 nm and several micrometers, respectively. The corresponding highresolution TEM image and the fast Fourier transform (FFT) electron diffraction pattern of the marked area are highlighted in Figure 1b, indicating the [301] growth direction of the  $\gamma$ -phase single-crystal nanowire. Figure 1c is the EDS spectrum, and a table of indium/selenium ratio is in the inset, revealing that the ratio of indium and selenium was  $\sim$ 2:3. The XRD pattern also confirms that the as-grown In<sub>2</sub>Se<sub>3</sub> nanowires were  $\gamma$ -phase, which is stable at room temperature and suitable for the phase change memory

application as compared with  $\beta$ ,  $\delta$ , and  $\kappa$ , as shown in Supporting Information Figure S1. Figure 1d is the schematic crystal structure of the  $\gamma$ -phase In<sub>2</sub>Se<sub>3</sub>.

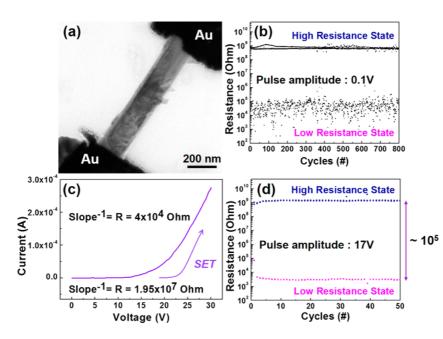

To understand the phase change switching behavior of In<sub>2</sub>Se<sub>3</sub> nanowire memory devices, a series of electrical measurements were performed. Figure 2 shows the typical TEM image and electrical characteristics of several Au/In<sub>2</sub>Se<sub>3</sub> nanowire/Au memory devices. The endurance of 800 cycles under a constant 0.1 V readout demonstrates that the resistance was  $10^9 \ \Omega$  at the high-resistance state, while the resistance was around  $10^4$  to  $10^5 \Omega$  at the low-resistance state. Although the low-resistance state fluctuates, the ratio of the amorphous and crystalline state still remains at 4 orders of magnitude among these devices. The corresponding RESET process is shown in Supporting Information Figure S2. To switch from the amorphous to singlecrystalline state, the dc voltage sweep mode was applied (Figure 2c). The resistance changed from  $1.95 \times 10^7$  to  $4 \times 10^4 \Omega$  during a voltage sweep from 0 to 25 V. In this case, 5.6  $\mu$ m electrode spacing would result in high-threshold SET voltage. The TEM images in the inset depict the structure evolution of the corresponding SET process. For the RESET process, a pulsed mode was applied to switch the device to induce a fast and sequence-like quench. If the crystal would have time to recrystallize, the amorphism process would fail.<sup>7,15–20</sup> The repeated switching of individual In<sub>2</sub>Se<sub>3</sub> nanowire memory devices is shown in Figure 2d, while the  $R_{OFF}/R_{ON}$  ratio was stable for 10<sup>5</sup> orders under a constant 17 V readout. The evolution of atomic structure and SAED pattern varies in different devices,

Figure 1. (a) TEM image of an  $\ln_2Se_3$  nanowire of several micrometers in length and 50 nm in diameter. (b) High-resolution transmission electron microscope (HRTEM) image of the marked area in (a). The inset shows the corresponding FFT electron diffraction pattern with [-1-23] zone axis. (c) EDS spectrum with the corresponding atomic percentage of In and Se in the inset. (d) Schematic crystal structure of  $\gamma$ -phase  $\ln_2Se_3$  nanowires.

VOL. 8 • NO. 9 • 9457-9462 • 2014 A

Figure 2. (a) TEM image of a Au/ln<sub>2</sub>Se<sub>3</sub> nanowire/Au memory device. (b) Endurance test under a constant 0.1 V readout. (c) Typical current–voltage measurement by voltage sweep to SET the ln<sub>2</sub>Se<sub>3</sub> nanowire memory. (d) ln<sub>2</sub>Se<sub>3</sub> nanowire memory device measured by pulsed mode to RESET under a constant 17 V readout with  $10^5 R_{OFF}/R_{ON}$  ratio.

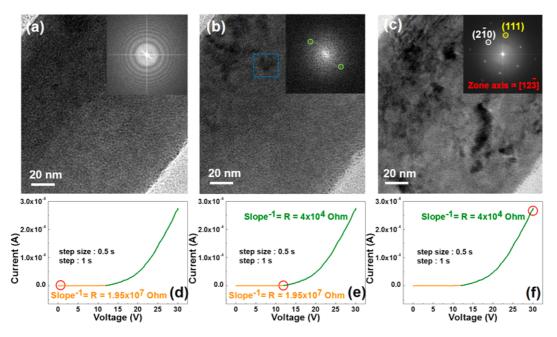

Figure 3. TEM images of the (a) original state, (b) crystalline state, and (c) single-crystalline state of the  $\ln_2$ Se<sub>3</sub> nanowire during phase transformation by dc voltage sweep mode to SET for a PCRAM device. (d-f) Corresponding current-voltage measurements.

depending on the pulse amplitude and width. The results of electrical measurements in Figure 2 show that the  $In_2Se_3$  nanowire is a potential candidate for a phase change material.

Figure 3a - c present the structure evolution during a SET process, and the corresponding dc voltage sweepmode behavior is highlighted with a red circle in Figure 3d-f.<sup>6</sup> During the process, which is shown in Supporting Information Video S1, the phase of the In<sub>2</sub>Se<sub>3</sub> nanowire transformed from an amorphous state to a single-crystalline state, and the inset is the corresponding FFT electron diffraction pattern. Initially, the resistance of  $\ln_2Se_3$  nanowire was  $1.95 \times 10^7 \Omega$ . It was transformed by ion implantation; with the subelectrodes fabricated by focus ion beam technology (FIB), the ion implantation (30 keV) at a higher dose may induce a phase transformation to an amorphous state.<sup>21</sup> After applying 12.5 V, the  $\ln_2Se_3$  nanowire was partly crystallized. Finally, the  $\ln_2Se_3$  nanowire transformed into single crystalline with a [12–3] zone axis

VOL. 8 • NO. 9 • 9457-9462 • 2014

A

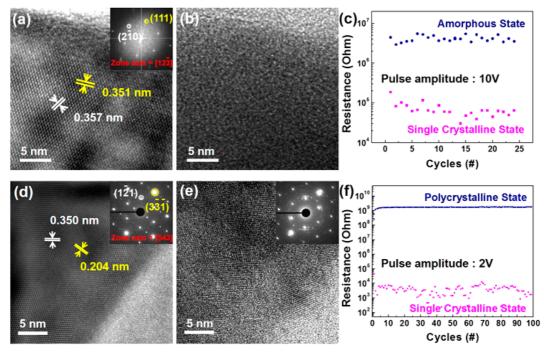

Figure 4. Phase transformation by pulsed mode switching to RESET the  $In_2Se_3$  nanowire PCRAM. The  $In_2Se_3$  nanowire changed from (a) single crystalline to (b) amorphous state. (d) Another example of the transformation from single crystalline state to (e) polycrystalline state after switching. (c and f) Corresponding electrical measurements, respectively.

after 25 V was applied. Meanwhile, its resistance was decreased to 4  $\times$  10<sup>4</sup>  $\Omega$ . This result demonstrated that the SET process was caused by the phase change from an amorphous state to a single-crystalline state.

For phase change memory materials, chalcogenide compounds have already exhibited quick switching ability.<sup>1,6-8,22-26</sup> In a SET transition, nucleation and growth processes are essential to the crystallization. When the voltage is applied, the duration time should be long enough to generate the heat for nucleation and growth. Then the material will transform and reach the low-resistance state. Thus, the temperature must be higher than its recrystallization temperature. Therefore, the dc voltage sweep mode was selected to apply in our experiments. From these images, it can be found that the nucleation and growth process occurred at low bias. The resistance decreased dramatically owing to full recrystallization and Joule heating. During the RESET-SET transition process, the temperature must be higher than the crystalline temperature and lower than the melting temperature; otherwise, the material cannot turn into the low-resistance state.<sup>19,27,28</sup> In our In<sub>2</sub>Se<sub>3</sub> nanowire memory device, the distance between two electrodes was 5.6  $\mu$ m, which is much longer than that of other reports, resulting in a larger threshold voltage of 25 V. This result also indicates that the magnitude of the electric field is another important factor for the phase change material to obtain the switching energy.

The pulsed mode was applied to RESET the  $In_2Se_3$  nanowire memory in order to avoid recrystallization. During the process, the pulse width was set at 0.1 s in our study due to the instrumental limit. Figure 4a illustrates another example of single-crystalline In<sub>2</sub>Se<sub>3</sub> nanowire with a [12-3] zone axis. After applying a pulse of 10 V for several cycles, the In<sub>2</sub>Se<sub>3</sub> nanowire transformed into an amorphous state as shown in Figure 4b, and its resistance increased to  $10^6 \Omega$ . The corresponding electrical characteristic is shown in Figure 4c. We used a high, 200 keV electron dose. According to Figure S2, the phase transformed at many parts, but only the section pointed out by the red arrow was focused. The magnification was set at 600k. After the voltage was applied, the magnification was set at 25k to observe the evolution of the nanowires, showing that the phase change section appeared not only under the electron beam but also without it. Therefore, the electron beam has a negligible or no effect on the phase transition. Figure 4d illustrates another RESET example with a different zone axis, transforming into a polycrystalline state (Figure 4e and the corresponding video as shown in Supporting Information Videos S2) by a pulse of 2 V. The corresponding switching behavior and the endurance are shown in Figure 4f. The endurance was tested for 100 cycles with a stable  $R_{OFF}/R_{ON}$  ratio (10<sup>6</sup>). Further investigations can be found in the Supporting Information (Figures S3 to S5 and Videos S2 to S4). From these results, a higher  $R_{OFF}/R_{ON}$  ratio from single-crystalline switching to polycrystalline was found. The higher resistance in the polycrystalline state compared with the amorphous state may result from the full transformation of the polycrystalline state rather than the partial transformation to the amorphous state in the nanowire. For a

VOL.8 • NO.9 • 9457-9462 • 2014

JAI

longer pulse width, a much higher voltage should be applied to completely transform the nanowire into an amorphous state.<sup>16</sup> Grain boundary scattering may be another reason for the higher resistance of the polycrystalline state. While the grain size is smaller than or similar to the electron mean free path, the grain boundary will induce electron scattering, which will increase the resistivity of the polycrystalline nanowires.<sup>29–31</sup> Thus, the  $R_{OFF}/R_{ON}$  ratio from singlecrystalline switching to the amorphous state in our study would be low.

In the SET-RESET transition, the amorphization was believed to be the melt-quench mechanism. The In<sub>2</sub>Se<sub>3</sub> material should be heated quickly to high temperature and then rapidly cooled, so that the atoms can maintain disorder to reach an amorphous state with high resistance. Therefore, the pulsed mode with high amplitude and short pulse width was selected to RESET the  $In_2Se_3$  phase change memory.<sup>7,17,28,32,33</sup> To reach a high temperature, a strong electric field would be necessary. This means that a stronger electric field can lead to a higher level of amorphization.<sup>4</sup> In Figure 4c and f, the pulse amplitudes were different. The higher pulse amplitude would cause the phase transition to be the amorphous state, while a lower one would induce the polycrystalline state. On comparison with the polycrystalline state and amorphous state for a RESET, the former was growth-dominated, while the latter was nucleation-dominated. Thus, a higher pulse voltage should be applied to the former to grow. Under the condition of long pulse width and small pulse amplitude, the temperature was not high enough to reach a crystalline state immediately, and the lowresistance state would be less stable<sup>15,34</sup> (more details

in Supporting Information Figures S3 to S5). In previous studies, a RESET to polycrystalline state has never been found, which may be caused by the longer pulse width. Under this condition, the temperature was high enough to melt the phase change material without a large pulse amplitude. Meanwhile, the longer pulse width would result in the annealing process instead of a quench process and arrange the atoms. As the In<sub>2</sub>Se<sub>3</sub> nanowire was partly transformed from single crystalline to polycrystalline, the larger pulse amplitude made the large area transform to polycrystalline. Furthermore, due to the induction of higher temperature, the grain size was larger while the larger pulse amplitude was applied (more details in Supporting Information Figure S6). Our observation provides the evidence for the correlation between electric behaviors of SET/ RESET processes and the evolution of nanostructures. Apparently, the pulse width and amplitude, which induce different magnitudes of electric fields, will affect the transformation from single crystalline to different phases.

#### CONCLUSIONS

In conclusion, we have fabricated In<sub>2</sub>Se<sub>3</sub> nanowirebased phase change memory devices of high resistivity ratio and lower programming current. The devices were switched by dc voltage sweep mode and pulsed mode. We observed the structural evolution of the In<sub>2</sub>Se<sub>3</sub> nanowire by *in situ* TEM and found that different pulse amplitudes and widths would result in phase transformation to polycrystalline or amorphous states. This study is expected to enhance the writing speed, retention, and endurance of PCRAM for future applications.

## **METHODS**

$In_2Se_3$  nanowires were synthesized in a vacuum furnace by the vapor—liquid—solid mechanism. A 0.82 g amount of selenium powder was placed upstream, while 1.2 g of indium shot was placed downstream with a 2 nm Au coated silicon substrate placed nearby. The temperature was kept for 2 h at 240 and 600 °C, respectively. The vacuum of the system was kept at 1 Torr with 200 sccm argon flow. After the growth processes, In\_2Se\_3 nanowires were grown on the substrates.

A 30 nm  $SiO_2$  and a 60 nm  $Si_3N_4$  layer were deposited on the Si substrate by a low-pressure chemical vapor deposition system. The region at the bottom window and the main electrode at the top were defined by photolithography. Then the bottom region was etched with KOH solution, leaving a Si<sub>3</sub>N<sub>4</sub> window for TEM inspection. A 20 nm Ti and a 40 nm Au layer were deposited by an electron gun evaporation system (E-gun) as the main electrode. A 30 nm Ti and 120 nm Au subelectrode were fabricated by the electron-beam lithography process and E-gun to form the In<sub>2</sub>Se<sub>3</sub>-PCRAM. The sample fabrication process and the corresponding SEM image of the device are shown in Supporting Information Figure S7. Subelectrodes were also fabricated by FIB, and a 100 nm Pt layer was deposited. The subelectrodes of different metals, Au and Pt, did not influence the electrical behavior due to the following two points. The first one is that Au and Pt are inert metals that will not react with  $ln_2Se_3$  nanowires. The other one is that the resistance of  $ln_2Se_3$  nanowires was about 10<sup>4</sup> ohm for all the electrodes. According to our previous experiments on nanowire electrical measurements, the order of resistance was the same with Au and Pt as subelectrodes. *In situ* TEM observation was carried out in a JEOL ARM-200FTH TEM, which was equipped with a video recorder with a 1/30 s time resolution and EDS. The *IV* switching behavior was operated by Protochips Aduro 300.<sup>35–37</sup>

*Conflict of Interest:* The authors declare no competing financial interest.

Supporting Information Available: Identification of  $In_2Se_3$  nanowires, in situ TEM images, and electrical measurements as supplementary online materials present the observation of the  $In_2Se_3$ -PCRAM during the RESET process. In situ TEM videos provide direct evidence of the  $In_2Se_3$  nanowire phase transformation processes. This material is available free of charge via the Internet at http://pubs.acs.org.

Acknowledgment. The authors acknowledge the support by the Ministry of Science and Technology through grants 102-2221-E-009-039, 100-2628-E-009-023-MY3, 103-2221-E-009-222-MY3, and 102-2221-E-006-077-MY3.

### **REFERENCES AND NOTES**

- Baek, C. K.; Kang, D.; Kim, J.; Jin, B.; Rim, T.; Park, S.; Meyyappan, M.; Jeong, Y. H.; Lee, J. S. Improved Performance of In<sub>2</sub>Se<sub>3</sub> Nanowire Phase-Change Memory with SiO<sub>2</sub> Passivation. *Solid-State Electron*. **2013**, *80*, 10–13.

- Jin, B.; Kang, D.; Kim, J.; Meyyappan, M.; Lee, J. S. Thermally Efficient and Highly Scalable In<sub>2</sub>Se<sub>3</sub> Nanowire Phase Change Memory. J. Appl. Phys. **2013**, *113*, 164303.

- Lee, H.; Kang, D. H.; Tran, L. Indium Selenide (In<sub>2</sub>Se<sub>3</sub>) Thin Film for Phase-Change Memory. *Mater. Sci. Eng.*: B 2005, 119, 196–201.

- Mafi, E.; Soudi, A.; Gu, Y. Electronically Driven Amorphization in Phase-Change In<sub>2</sub>Se<sub>3</sub> Nanowires. J. Phys. Chem. C 2012, 116, 22539–22544.

- Tao, X.; Gu, Y. Crystalline-Crystalline Phase Transformation in Two-Dimensional In<sub>2</sub>Se<sub>3</sub> Thin Layers. *Nano Lett.* **2013**, *13*, 3501–3505.

- Lee, H.; Kim, Y. K.; Kim, D.; Kang, D. H. Switching Behavior of Indium Selenide-Based Phase-Change Memory Cell. *IEEE Trans. Magn.* 2005, *41*, 1034–1036.

- 7. Meister, S.1-D Chalcogenide Nanomaterials for Electronics: Phase-Change Memory and Topological Insulators. Ph.D. Thesis, Stanford University, 2010.

- Chung, A.; Deen, J.; Lee, J. S.; Meyyappan, M. Nanoscale Memory Devices. *Nanotechnology* 2010, 21, 412001.

- Han, N.; Kim, S. I.; Yang, J. D.; Lee, K.; Sohn, H.; So, H. M.; Ahn, C. W.; Yoo, K. H. Phase-Change Memory in Bi<sub>2</sub>Te<sub>3</sub> Nanowires. *Adv. Mater.* 2011, *23*, 1871–1875.

- Lee, S. H.; Jung, Y.; Agarwal, R. Highly Scalable Non-Volatile and Ultra-Low-Power Phase-Change Nanowire Memory. *Nat. Nanotechnol.* 2007, 2, 626–630.

- Nam, S. W.; Chung, H. S.; Lo, Y. C.; Qi, L.; Li, J.; Lu, Y.; Johnson, a. T. C.; Jung, Y.; Nukala, P.; Agarwal, R. Electrical Wind Force-Driven and Dislocation-Templated Amorphization in Phase-Change Nanowires. *Science* **2012**, *336*, 1561–1566.

- Yu, B.; Ju, S.; Sun, X.; Ng, G.; Nguyen, T. D.; Meyyappan, M.; Janes, D. B. Indium Selenide Nanowire Phase-Change Memory. *Appl. Phys. Lett.* **2007**, *91*, 133119.

- Nukala, P.; Agarwal, R.; Qian, X.; Jang, M. H.; Dhara, S.; Kumar, K.; Johnson, A. T. C.; Li, J.; Agarwal, R. Direct Observation of Metal–Insulator Transition in Single-Crystalline Germanium Telluride Nanowire Memory Devices Prior to Amorphization. *Nano Lett.* **2014**, *14*, 2201–2209.

- Wełnic, W.; Pamungkas, A.; Detemple, R.; Steimer, C.; Blügel, S.; Wuttig, M. Unravelling the Interplay of Local Structure and Physical Properties in Phase-Change Materials. *Nat. Mater.* 2005, *5*, 56–62.

- Loke, D.; Lee, T. H.; Wang, W. J.; Shi, L. P.; Zhao, R.; Yeo, Y. C.; Chong, T. C.; Elliott, S. R. Breaking the Speed Limits of Phase-Change Memory. *Science* **2012**, *336*, 1566–1569.

- Meister, S.; Kim, S.; Cha, J. J.; Wong, H. S. P.; Cui, Y. *In Situ* Transmission Electron Microscopy Observation of Nanostructural Changes in Phase-Change Memory. *ACS Nano* **2011**, *5*, 2742–2748.

- Hegedüs, J.; Elliott, S. R. Microscopic Origin of the Fast Crystallization Ability of Ge-Sb-Te Phase-Change Memory Materials. *Nat. Mater.* **2008**, *7*, 399–405.

- Raoux, S.; Burr, G. W.; Breitwisch, M. J.; Rettner, C. T.; Shelby, R. M.; Salinga, M.; Krebs, D.; Chen, S. H.; Lung, H. L.; Lam, C. H. Phase-Change Random Access Memory: A Scalable Technology. *IBM J. Res. Dev.* **2008**, *52*, 465–479.

- Hamann, H. F.; O'Boyle, M.; Martin, Y. C.; Rooks, M.; Wickramasinghe, H. K. Ultra-High-Density Phase-Change Storage and Memory. *Nat. Mater.* **2006**, *5*, 383–387.

- Kolobov, A. V.; Fons, P.; Frenkel, A. I.; Ankudinov, A. L.; Tominaga, J.; Uruga, T. Understanding the Phase-Change Mechanism of Rewritable Optical Media. *Nat. Mater.* 2004, 3, 703–708.

- Raoux, S.; Cohen, G. M.; Shelby, R. M.; Cheng, H.-Y.; Madan, A.; Ott, J.; Sweet, J. L. J. In E⊠ect of Ion Implantation on Crystallization Properties of Phase Change Materials; Proceedings of E\*PCOS, Milan, Italy, Sept 5–7, 2010.

- Lencer, D.; Salinga, M.; Grabowski, B.; Hickel, T.; Neugebauer, J.; Wuttig, M. A Map for Phase-Change Materials. *Nat. Mater.* **2008**, *7*, 972–977.

- Ohara, K.; Temleitner, L.; Sugimoto, K.; Kohara, S.; Matsunaga, T.; Pusztai, L.; Itou, M.; Ohsumi, H.; Kojima, R.; Yamada, N.; *et al.* The Roles of the Ge-Te Core Network and the Sb-Te Pseudo Network during Rapid Nucleation-Dominated Crystallization of Amorphous Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>. *Adv. Funct. Mater.* **2012**, *22*, 2251–2257.

- Xiong, F.; Bae, M. H.; Dai, Y.; Liao, A. D.; Behnam, A.; Carrion, E. A.; Hong, S.; Ielmini, D.; Pop, E. Self-Aligned Nanotube-Nanowire Phase Change Memory. *Nano Lett.* **2013**, *13*, 464–469.

- Park, W. I.; You, B. K.; Mun, B. H.; Seo, H. K.; Lee, J. Y.; Hosaka, S.; Yin, Y.; Ross, C. a.; Lee, K. J.; Jung, Y. S. Self-Assembled Incorporation of Modulated Block Copolymer Nanostructures in Phase-Change Memory for Switching Power Reduction. ACS Nano 2013, 7, 2651–2658.

- Milliron, D. J.; Raoux, S.; Shelby, R. M.; Jordan-Sweet, J. Solution-Phase Deposition and Nanopatterning of GeSbSe Phase-Change Materials. *Nat. Mater.* 2007, *6*, 352–356.

- Raoux, S.; Jordan-Sweet, J. L.; Kellock, A. J. Crystallization Properties of Ultrathin Phase Change Films. J. Appl. Phys. 2008, 103, 114310.

- Simpson, R. E.; Krbal, M.; Fons, P.; Kolobov, A. V.; Tominaga, J.; Uruga, T.; Tanida, H. Toward the Ultimate Limit of Phase Change in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>. *Nano Lett.* **2010**, *10*, 414–419.

- Mayadas, A. F.; Shatzkes, M. Electrical-Resistivity Model for Polycrystalline Films: The Case of Arbitrary Reflection at External Surfaces. *Phys. Rev. B* 1970, *1*, 1382–1389.

- Rossnagel, S. M.; Kuan, T. S. Alteration of Cu Conductivity in the Size Effect Regime. J. Vac. Sci. Technol. B 2004, 22, 240–247.

- Zhu, Y. F.; Lang, X. Y.; Zheng, W. T.; Jiang, Q. Electron Scattering and Electrical Conductance in Polycrystalline Metallic Films and Wires: Impact of Grain Boundary Scattering Related to Melting Point. ACS Nano 2010, 4, 3781–3788.

- Lankhorst, M. H. R.; Ketelaars, B. W. S. M. M.; Wolters, R. A. M. Low-Cost and Nanoscale Non-Volatile Memory Concept for Future Silicon Chips. *Nat. Mater.* 2005, *4*, 347–352.

- Gyanathan, A.; Yeo, Y. C. Two-Bit Multi-Level Phase Change Random Access Memory with a Triple Phase Change Material Stack Structure. J. Appl. Phys. 2012, 112, 104504.

- Welnic, W.; Wuttig, M. Reversible Switching in Phase-Change Materials. *Mater. Today* 2008, 11, 20–27.

- Huang, Y. T.; Yu, S. Y.; Hsin, C. L.; Huang, C. W.; Kang, C. F.; Chu, F. H.; Chen, J. Y.; Hu, J. C.; Chen, L. T.; He, J. H.; *et al. In Situ* TEM and Energy Dispersion Spectrometer Analysis of Chemical Composition Change in ZnO Nanowire Resistive Memories. *Anal. Chem.* **2013**, *85*, 3955–3960.

- Chen, J. Y.; Hsin, C. L.; Huang, C. W.; Chiu, C. H.; Huang, Y. T.; Lin, S. J.; Wu, W. W.; Chen, L. J. Dynamic Evolution of Conducting Nanofilament in Resistive Switching Memories. *Nano Lett.* **2013**, *13*, 3671–3677.

- Huang, C. W.; Chen, J. Y.; Chiu, C. H.; Wu, W. W. Revealing Controllable Nanowire Transformation through Cationic Exchange for RRAM Application. *Nano Lett.* **2014**, *14*, 2759–2763.